User's Manual for A Sequencing LSI for Stepper Motors

# PCD4511/4521/4541

**NPM** : Nippon Pulse Motor Co., Ltd.

# A Sequencing LSI for Stepper Motors PCD4511/4521/4541

The PCD4511/4521/4541 are excitation control LSIs designed for 2-phase stepper motors. With just one of these LSIs and a stepper motor driver IC (e.g. NP-7026), you can easily construct a stepper motor control system.

Data and commands entered from a CPU enable this LSI to control the speed and position of a stepper motor. Since the LSI has a pulse signal generation circuit, it can also control a motor driver that relies on the number of pulses supplied.

Users can select the 4511 (single-axis model), 4521 (2 axes model), or 4541 (4 axes model) PCD to drive their motors.

# 1. Functions

- 1) Continuous operation (constant speed, linear and S-curve acceleration and deceleration).

- 2) Preset operation (constant speed, linear and S-curve acceleration and deceleration).

- 3) Zero return operation (constant speed, linear and S-curve acceleration and deceleration).

- 4) Timer operation

- 5) Excitation output sequencing for 2-phase stepper motors

- 2-2 phase / 1-2 phase

- Unipolar / bipolar

- 6) Idling pulse output (0 to 7 pulses)

- 7) Deceleration by specifying a ramping-down point.

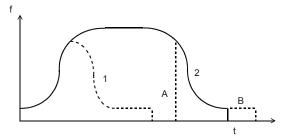

- 8) Change speed while operating.

- 9) Change to constant speed in the middle of an acceleration or deceleration.

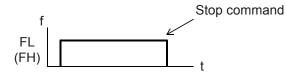

- 10) Deceleration stop and immediate stop.

- 11) Output external start and stop signals for other equipment.

- 12) Input external signals from other equipment ( $\pm$ SD,  $\pm$ EL, ORG)

- 13) Output an interrupt signal ( $\overline{INT}$ ).

- 14) Status monitoring signal for each operation.

- 15) Available in standard mounting packages

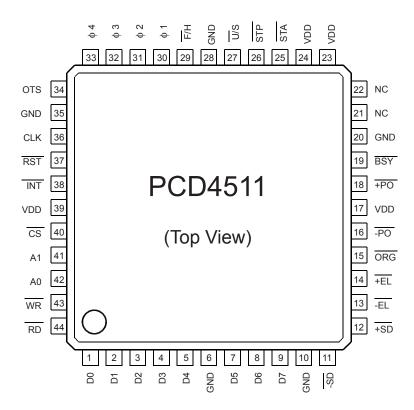

- PCD4511: 44-pin QFP

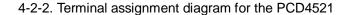

- PCD4521: 64-pin QFP

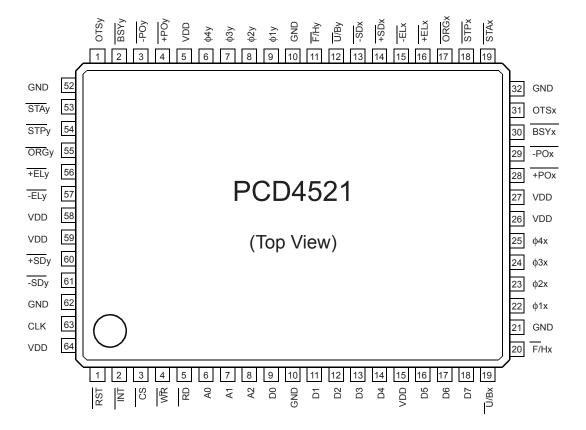

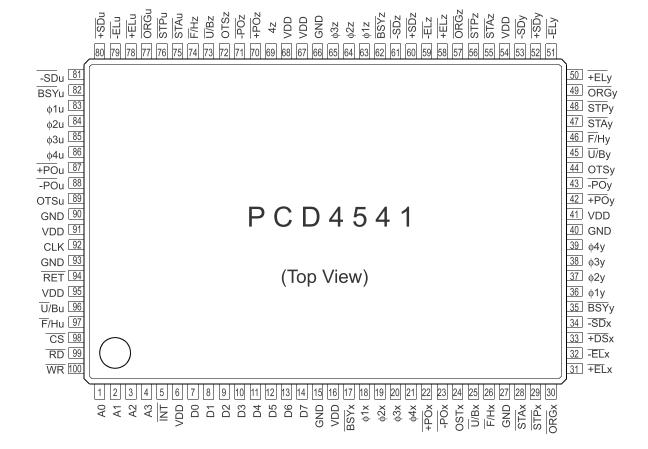

- PCD4541: 100-pin QFP

# 2. Software settings

# 2-1. Address lines

Relationship between address lines (A1, A0) and  $\overline{RD}$ ,  $\overline{WR}$ , and  $\overline{CS}$ .

| CS | RD | $\overline{WR}$ | A1 | A0 | Detail                                         |  |  |

|----|----|-----------------|----|----|------------------------------------------------|--|--|

| L  | Н  | L               | L  | L  | Data bus -> Command buffer                     |  |  |

| L  | н  | L               | ∟  | Н  | Data bus -> Register (bits 7 to 0: lower bit)  |  |  |

| L  | Н  | L               | Н  | L  | Data bus -> Register (bit 15 to 8: Medium bit) |  |  |

| L  | Н  | L               | Н  | Н  | Pata bus -> Register (bit 23 to 16: Upper bit) |  |  |

| L  | L  | Н               | L  | L  | Pata bus <- Status 0                           |  |  |

| L  | L  | Н               | L  | Н  | Data bus <- Internal data (lower)              |  |  |

| L  | L  | Н               | Н  | L  | ata bus <- Internal data (medium) Reading      |  |  |

| L  | L  | Н               | Н  | Н  | Data bus <- Internal data (upper)              |  |  |

Relationship between address lines (A3, A2) and the axes controlled by a PCD4521/4541.

| PCD4521       |        |        |  | PCD4541        |        |        |        |        |

|---------------|--------|--------|--|----------------|--------|--------|--------|--------|

| A2 setting    | A2=0   | A2=1   |  | A2, A3 setting | A3=0,  | A3=0,  | A3=1,  | A3=1,  |

|               |        |        |  |                | A2=0   | A2=1   | A2=0   | A2=1   |

| Selected axis | X axis | Y axis |  | Selected axis  | X axis | Y axis | Z axis | U axis |

# 2-2. Command buffer

In order to operate this LSI, data is written into the command buffer and each data register through the 8-bit data bus.

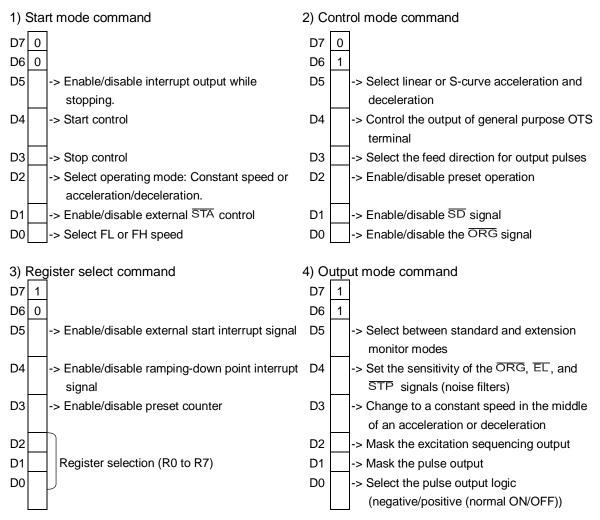

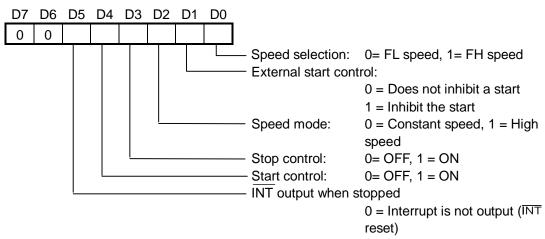

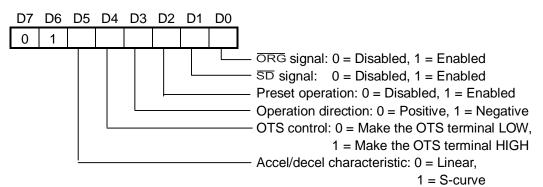

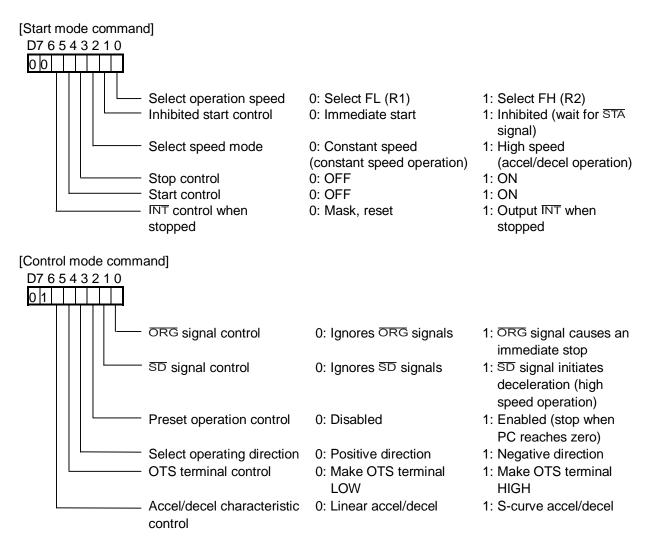

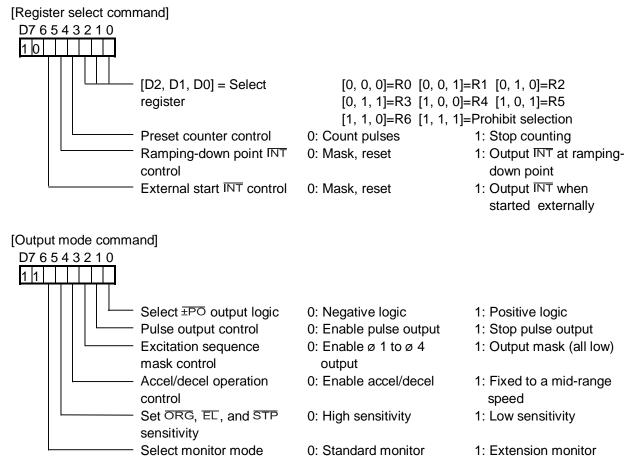

Commands can be classified into four groups, and the upper 2 bits in each command are used to specify the group. Each command is latched until the same group command is written a second time. Each bit in a command represents a specific function. Functions do not have individual commands.

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

| C1 | C0 |    |    |    |    |    |    |

| C1 | C0 | Command group   |

|----|----|-----------------|

| 0  | 0  | Start mode      |

| 0  | 1  | Control mode    |

| 1  | 0  | Select register |

| 1  | 1  | Output mode     |

2-3. Bit details for each command

#### 2-4. Table of registers

| labio |    | Y  |          |                                      |       |            | 1             |

|-------|----|----|----------|--------------------------------------|-------|------------|---------------|

| D2    | D1 | D0 | Register | Details                              | R/W   | Bit length | Setting range |

| 0     | 0  | 0  | R0       | Preset counter data                  | R/W   | 24         | 0 to FFFFFF   |

| 0     | 0  | 1  | R1       | FL speed                             | W (R) | 13         | 1 to 1FFF     |

| 0     | 1  | 0  | R2       | FH speed                             | W (R) | 13         | 1 to 1FFF     |

| 0     | 1  | 1  | R3       | Rate of accel/decel                  | W (R) | 10         | 2 to 3FF      |

| 1     | 0  | 0  | R4       | Magnification                        | W (R) | 10         | 2 to 3FF      |

| 1     | 0  | 1  | R5       | Ramping-down point                   | W (R) | 16         | 0 to FFFF     |

| 1     | 1  | 0  | R6       | Number of idling pulses              | W (R) | 3          | 0 to 7        |

| 1     | 1  | 1  | R7       | Environmental data<br>(PCD4541 only) | W (R) | 1          | 0 to (1)      |

\* D2, D1, and D0: Bits used to select the register

(R): Can be read by enabling the extension monitor

# 3. Examples of operation settings

3-1. Command setting example

This LSI is operated by specifying one of 4 types of commands and by entering values for registers R0 to R7.

- Specify the control mode command details (64<sub>HEX</sub>) --- Preset operation, S-curve rate of accel/decel, + direction, disable SD/ORG.

- 2) Specify the register select command details --- See the setting details in section 3-2 above.

- Specify the output mode command details (D1<sub>HEX</sub>) --- Excitation sequencing output, pulse output positive logic, enable filter.

- Specify the start command details (15<sub>HEX</sub>) --- Start and accelerate at FL speed, and operate at FH speed.

By specifying the start command, the LSI will start operation.

3-2. Example of setting a register

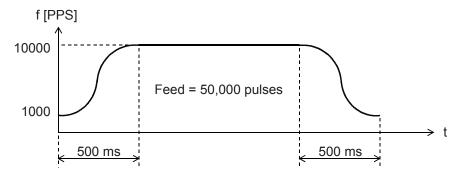

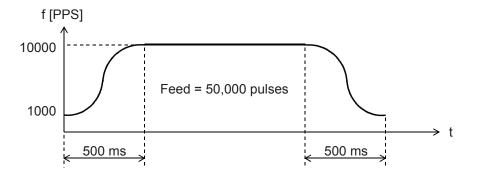

Example of an operating pattern

Initial speed (FL) = 1,000 PPS, operating speed (FH) = 10,000 PPS, accel/decel time = 500 mS, reference clock = 4.9152 MHz

1) Set the number of pulses as a preset amount (R0): Stop after outputting 50,000 pulses R0 = 50,000

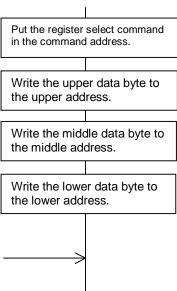

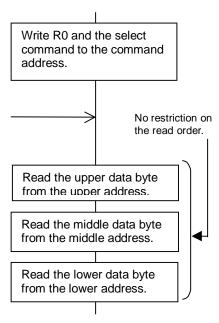

To write data into a register, first specify the register (R0) using the register select command  $(80_{HEX})$ . Then, write the data as three bytes in the following order: upper bits, middle bits, and lower bits.

2) Set the multiplication of the output frequency (R4): Select 2x for the LSI outputs (10,000 PPS in this example).

R4 set value =  $\frac{\text{Reference clock frequency [Hz]}}{\text{Magnification x 8192}} = \frac{4915200}{2 \times 8192} = 300$

<u>R4 = 30</u>0

3) Set the FL frequency (R1): Since the initial speed is set to 1,000 PPS in the 2x mode, R1 = 500.

- Set the FH frequency (R2): Since the initial speed is set to 10,000 PPS in the 2x mode, R2 = 5,000.

- 5) Set the accel/decel time constant (R3): Since S-curve accel/decel is selected with an accel/decel time of 500 mS.

[S-curve rate of accel/decel]

$$R3 = \frac{0.5 \times 4915200}{(5000 - 500) \times 2} = 273.07 = 273$$

<u>R3 =273</u>

6) Set the number of pulses for the ramping-down point (R5):

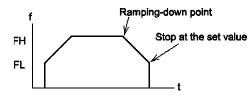

By setting the ramping-down point register (R5) while in the preset operation mode, you can specify the number of pulses remaining at which to start deceleration.

R5 set value [pulses] =  $\frac{((R2 \text{ set value})^2 - (R1 \text{ set value})^2) \times (R3 \text{ set value})}{(R4 \text{ set value}) \times 8192}$

[S-curve accel/decel]

$$R5 = \frac{(5000^2 - 500^2) \times 273}{300 \times 8192} = 2749.33 \approx 2750$$

R5=2750

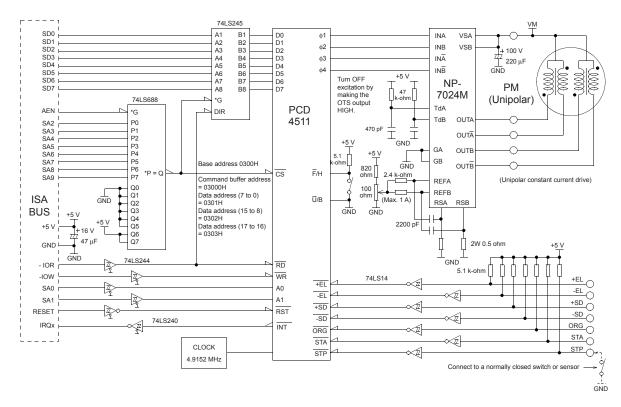

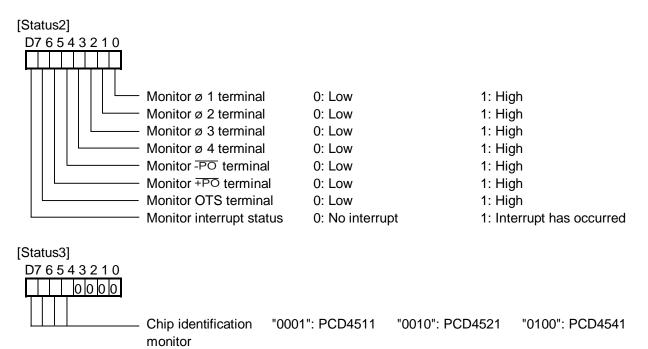

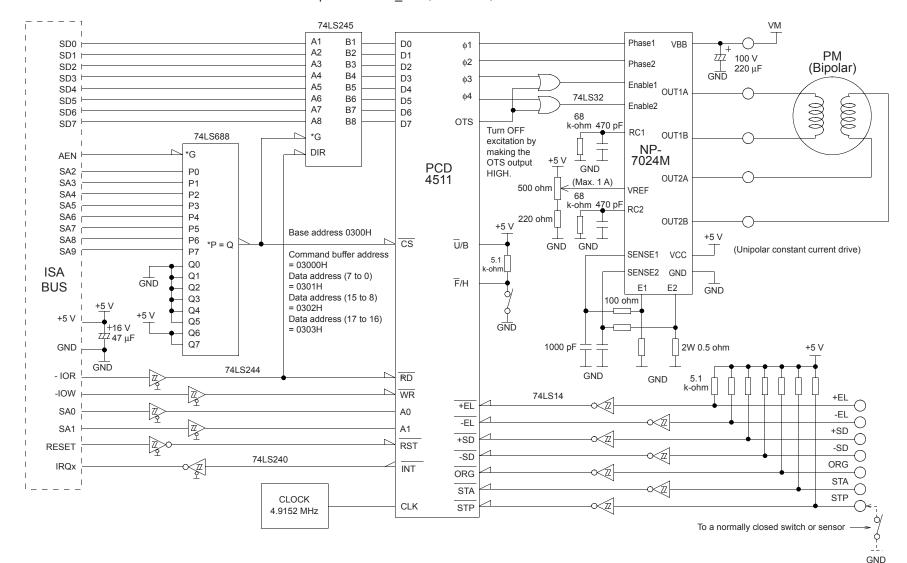

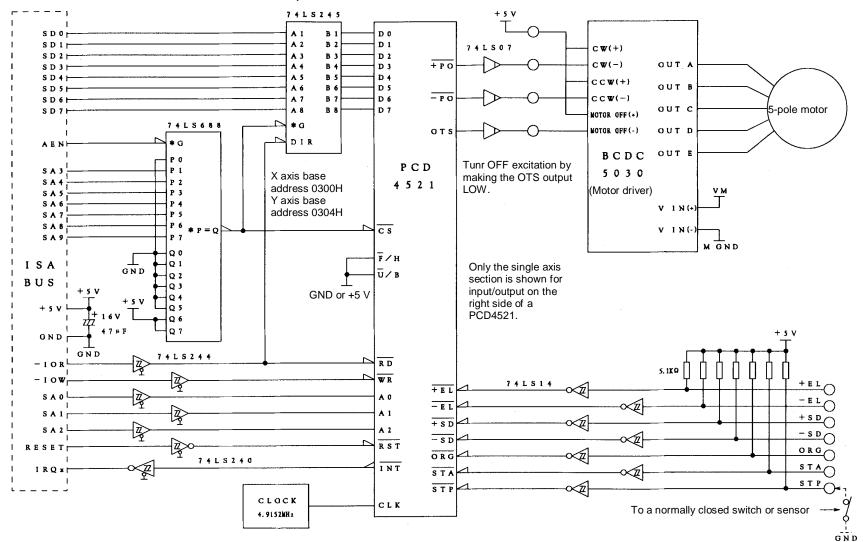

## 4. Connection example

Connection example using an ISA\_BUS -> PCD4511 -> NP-7024(6) M

**User's Manual**

for

A Sequencing LSI for Stepper Motors

# PCD4511/4521/4541

# Preface

Thank you for considering the use of our "PCD45X1 series."

Before using one of the PCD45X1 LSIs, read this manual carefully and become familiar with the product.

The "Handling precautions" for mounting these ICs are in the last part of this manual.

# Precautions

- 1) Transmission or copying of all or part of this manual is prohibited without prior written approval.

- 2) The specifications provided in this manual may be changed without prior notice to improve our product's performance or quality.

- 3) This manual was created with the utmost care. However, if you have any questions, find problems or believe important material is missing from the manual, please let us know.

- 4) NMP is not liable for any results of using this product, even if a problem or error has been reported.

# Description of the expressions and symbols used in this manual.

- 1. "x," "y," "z," and "u" on the terminal assignment drawings at the end of this manual or in parenthesis () in the terminal tables refer to the X axis, Y axis, Z axis, and U axis, respectively.

- 2. Terminals with a line above the terminal name, like RST, mean that the terminal uses negative logic (normally ON).

# Table of contents

| 1. Outline and features                            | 1  |

|----------------------------------------------------|----|

| 2. Specifications                                  | 1  |

| 3. Table of registers                              | 2  |

| 4. Hardware description                            |    |

| 4-1. Circuit block diagram                         | 3  |

| 4-2. Terminal assignment diagrams                  | 4  |

| 4-2-1. Terminal assignment diagram for the PCD4511 | 4  |

| 4-2-2. Terminal assignment diagram for the PCD4521 | 5  |

| 4-2-3. Terminal assignment diagram for the PCD4541 |    |

| 4-3. List of terminals                             |    |

| 4-3-1. List of terminals on the PCD4511            |    |

| 4-3-2. List of terminals on the PCD4521            |    |

| 4-3-3. List of terminals on the PCD4541            |    |

| 4-4. Description of each terminal                  |    |

| 4-4-1. <del>+</del> SD, - <u>SD</u>                |    |

| 4-4-2. <del>FEL</del> , - <del>EL</del>            |    |

| 4-4-3. ORG                                         |    |

| 4-4-4. STP                                         |    |

| 4-4-5. STA                                         |    |

| 4-4-6. +PO, -PO                                    |    |

| 4-4-7. Φ1, Φ2, Φ3, and Φ4<br>4-4-8. Ū/B            |    |

| 4-4-8. 0/В<br>4-4-9. F/H                           |    |

| 4-4-9. Г/П                                         |    |

| 4-4-10. 013<br>4-4-11. INT                         |    |

| 4-4-12. BSY                                        |    |

| 4-4-13. CLK                                        |    |

| 4-4-14. RST                                        |    |

| 4-4-15. CS                                         |    |

| 4-4-16. RD                                         |    |

| 4-4-17. WR                                         | 13 |

| 4-4-18. A0, A1, A2, and A3                         |    |

| 4-4-19. D0 to D7                                   |    |

| 4-4-20. VDD and GND                                | 13 |

| 4-4-21. NC [PCD4511 only]                          |    |

| 4-5. Initial (reset ) status                       | 13 |

| 4-6. CPU interface circuit block diagram           | 14 |

| 4-7. Precautions for designing hardware                                                                                                                                                                                                                                                                                                                                                        | 15                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 4-7-1. Input terminals                                                                                                                                                                                                                                                                                                                                                                         | 15                                                       |

| 4-7-2. Excitation sequencing                                                                                                                                                                                                                                                                                                                                                                   | 15                                                       |

| 5. Programming Description                                                                                                                                                                                                                                                                                                                                                                     | 16                                                       |

| 5-1. Addresses                                                                                                                                                                                                                                                                                                                                                                                 | -                                                        |

| 5-1-1. PCD4511 addresses                                                                                                                                                                                                                                                                                                                                                                       | 16                                                       |

| 5-1-2. PCD4521 addresses                                                                                                                                                                                                                                                                                                                                                                       | 16                                                       |

| 5-1-3. PCD4541 addresses                                                                                                                                                                                                                                                                                                                                                                       | 16                                                       |

| 5-2. Read and write the data register                                                                                                                                                                                                                                                                                                                                                          |                                                          |

| 5-2-1. Write procedures                                                                                                                                                                                                                                                                                                                                                                        |                                                          |

| 5-2-2. Read procedures                                                                                                                                                                                                                                                                                                                                                                         |                                                          |

| 5-3. Internal data monitor                                                                                                                                                                                                                                                                                                                                                                     | 18                                                       |

| 5-3-1. Reading Status                                                                                                                                                                                                                                                                                                                                                                          |                                                          |

| 5-3-2. Reading the register, command, and speed data                                                                                                                                                                                                                                                                                                                                           |                                                          |

| 5-4. Precautions when writing programs                                                                                                                                                                                                                                                                                                                                                         | 19                                                       |

| 5-4-1. Read/write data                                                                                                                                                                                                                                                                                                                                                                         | 19                                                       |

| 5-4-2. Data setting                                                                                                                                                                                                                                                                                                                                                                            | 20                                                       |

| 5-4-3. Preparation for starting                                                                                                                                                                                                                                                                                                                                                                | 20                                                       |

| 6. Description of functions                                                                                                                                                                                                                                                                                                                                                                    |                                                          |

| 6-1. Excitation sequencing of stepper motors                                                                                                                                                                                                                                                                                                                                                   | 21                                                       |

| 6-2. Speed pattern setting                                                                                                                                                                                                                                                                                                                                                                     |                                                          |

| 6-2-1. Speed setting                                                                                                                                                                                                                                                                                                                                                                           |                                                          |

| 6-2-2. Example of setting the acceleration/deceleration speed pattern                                                                                                                                                                                                                                                                                                                          |                                                          |

| 6-2-3. Setting the ramping-down point                                                                                                                                                                                                                                                                                                                                                          |                                                          |

| 6-2-4. Example of setting a ramping-down point (S-curve accel/decel)                                                                                                                                                                                                                                                                                                                           |                                                          |

| 6-3. Operating mode                                                                                                                                                                                                                                                                                                                                                                            | 24                                                       |

| 6-3-1. Continuous mode                                                                                                                                                                                                                                                                                                                                                                         |                                                          |

| 6-3-2. Preset mode                                                                                                                                                                                                                                                                                                                                                                             | 26                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

| 6-3-3. Zero return mode                                                                                                                                                                                                                                                                                                                                                                        |                                                          |

| 6-3-4. Timer mode                                                                                                                                                                                                                                                                                                                                                                              | 27                                                       |

| 6-3-4. Timer mode<br>6-4. Control function                                                                                                                                                                                                                                                                                                                                                     | 27<br>28                                                 |

| 6-3-4. Timer mode                                                                                                                                                                                                                                                                                                                                                                              | 27<br>28                                                 |

| <ul> <li>6-3-4. Timer mode</li> <li>6-4. Control function</li> <li>6-4-1. Idling pulse output</li> <li>6-4-2. External start signal</li> </ul>                                                                                                                                                                                                                                                 | 27<br>28<br>28<br>28                                     |

| <ul> <li>6-3-4. Timer mode</li> <li>6-4. Control function</li> <li>6-4-1. Idling pulse output</li> <li>6-4-2. External start signal</li> <li>6-4-3. External stop control</li> </ul>                                                                                                                                                                                                           | 27<br>28<br>28<br>28<br>29                               |

| <ul> <li>6-3-4. Timer mode</li> <li>6-4. Control function</li></ul>                                                                                                                                                                                                                                                                                                                            | 27<br>28<br>28<br>28<br>29<br>29                         |

| <ul> <li>6-3-4. Timer mode</li> <li>6-4. Control function</li> <li>6-4-1. Idling pulse output</li> <li>6-4-2. External start signal</li> <li>6-4-3. External stop control</li> <li>6-4-4. Excitation sequence output mask</li> <li>6-4-5. Pulse output logic</li> </ul>                                                                                                                        | 27<br>28<br>28<br>28<br>29<br>29<br>29                   |

| <ul> <li>6-3-4. Timer mode</li> <li>6-4. Control function</li> <li>6-4-1. Idling pulse output</li> <li>6-4-2. External start signal</li> <li>6-4-3. External stop control</li> <li>6-4-4. Excitation sequence output mask</li> <li>6-4-5. Pulse output logic</li> <li>6-4-6. External mechanical input control</li> </ul>                                                                      | 27<br>28<br>28<br>28<br>29<br>29<br>29<br>30             |

| <ul> <li>6-3-4. Timer mode</li> <li>6-4. Control function</li></ul>                                                                                                                                                                                                                                                                                                                            | 27<br>28<br>28<br>28<br>29<br>29<br>29<br>30<br>31       |

| <ul> <li>6-3-4. Timer mode</li> <li>6-4. Control function</li> <li>6-4-1. Idling pulse output</li> <li>6-4-2. External start signal</li> <li>6-4-3. External stop control</li> <li>6-4-4. Excitation sequence output mask</li> <li>6-4-5. Pulse output logic</li> <li>6-4-6. External mechanical input control</li> <li>6-4-7. Interrupt signal output</li> <li>6-5. Command buffer</li> </ul> | 27<br>28<br>28<br>28<br>29<br>29<br>29<br>30<br>31<br>32 |

| <ul> <li>6-3-4. Timer mode</li> <li>6-4. Control function</li></ul>                                                                                                                                                                                                                                                                                                                            | 27<br>28<br>28<br>29<br>29<br>29<br>30<br>31<br>32<br>32 |

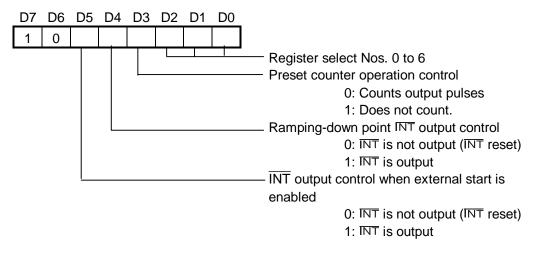

| 6-5-3. Register select command                                                                                                                                  |                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

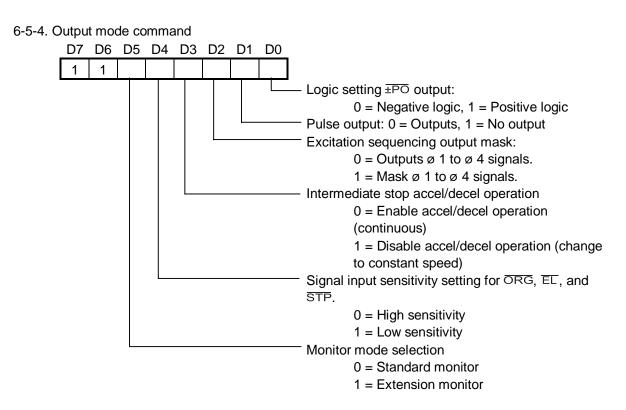

| 6-5-4. Output mode command                                                                                                                                      | 39                                                                                                                                           |

| 6-6. Registers                                                                                                                                                  | 41                                                                                                                                           |

| 6-6-1. R0 preset pulse counter (24 bits)                                                                                                                        | 41                                                                                                                                           |

| 6-6-2. R1: FL speed register (13 bits)                                                                                                                          | 41                                                                                                                                           |

| 6-6-3. R2: FH speed register (13 bits)                                                                                                                          | 41                                                                                                                                           |

| 6-6-4. R3: Accel/decel rate register (10 bits)                                                                                                                  | 42                                                                                                                                           |

| 6-6-5. R4: Magnification register (10 bits)                                                                                                                     | 42                                                                                                                                           |

| 6-6-6. R5: Ramping-down point register (16 bits)                                                                                                                | 42                                                                                                                                           |

| 6-6-7. R6: Idling pulse register (3-bit)                                                                                                                        | 42                                                                                                                                           |

| 6-6-8. R7: Environmental data register (1-bit)                                                                                                                  | 43                                                                                                                                           |

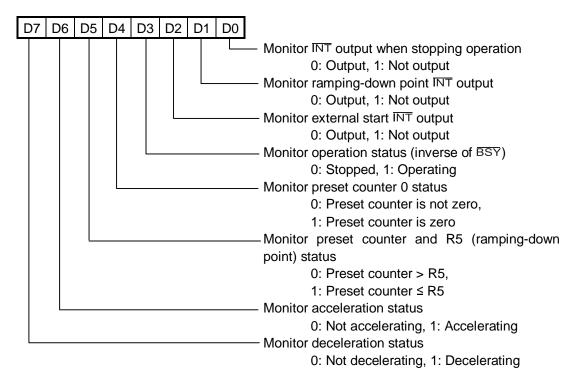

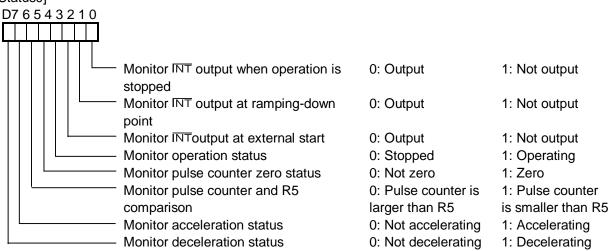

| 6-7. Status                                                                                                                                                     | 43                                                                                                                                           |

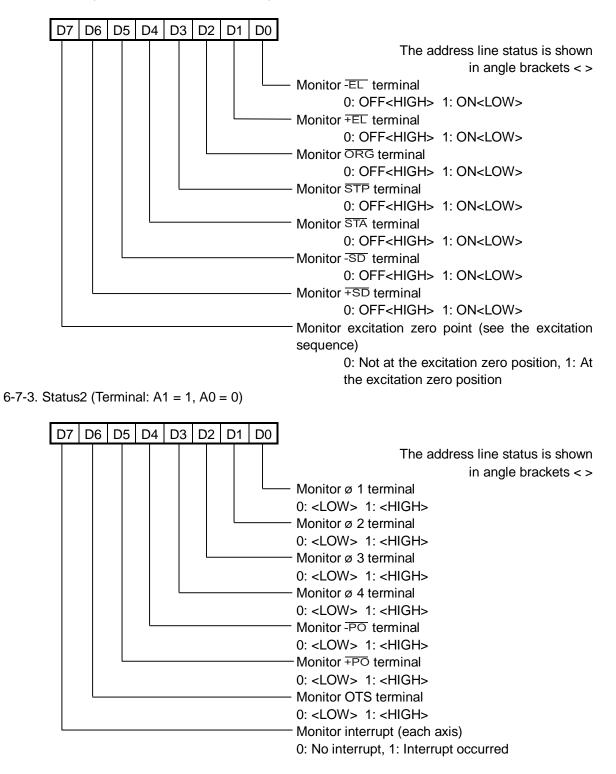

| 6-7-1. Status0 (address lines: A1 = 0, A0 = 0)                                                                                                                  | 44                                                                                                                                           |

| 6-7-2. Status1 (Address lines: A1 = 0, A0 = 1)                                                                                                                  |                                                                                                                                              |

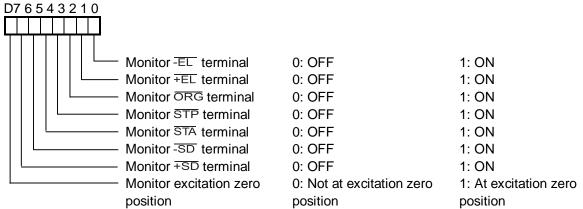

| 6-7-3. Status2 (Terminal: A1 = 1, A0 = 0)                                                                                                                       | 45                                                                                                                                           |

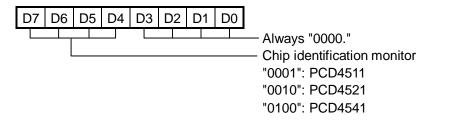

| 6-7-4. Status3 (Terminal: A1 = 1, A0 = 1)                                                                                                                       | 46                                                                                                                                           |

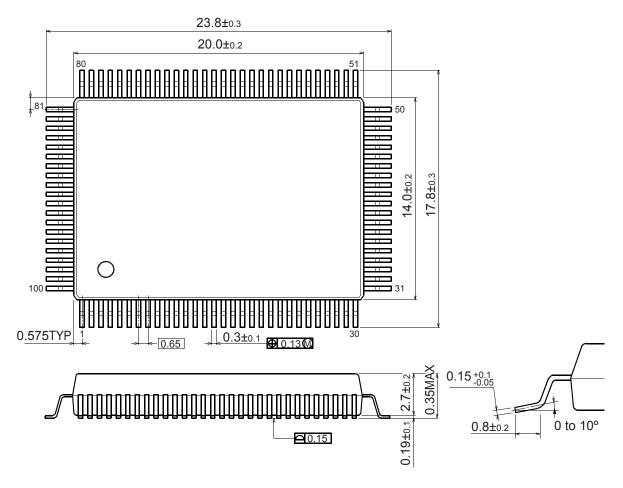

| 7. External dimensions                                                                                                                                          | 47                                                                                                                                           |

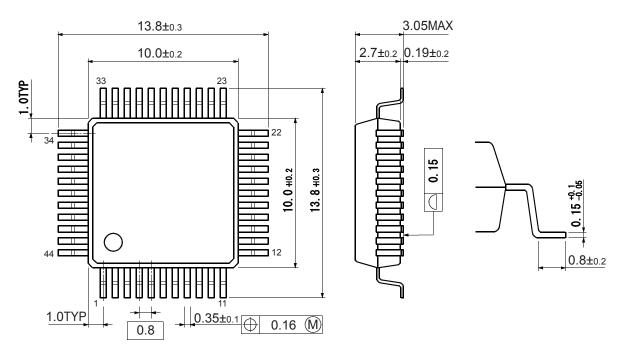

| 7-1. External dimensions of the PCD4511                                                                                                                         | 47                                                                                                                                           |

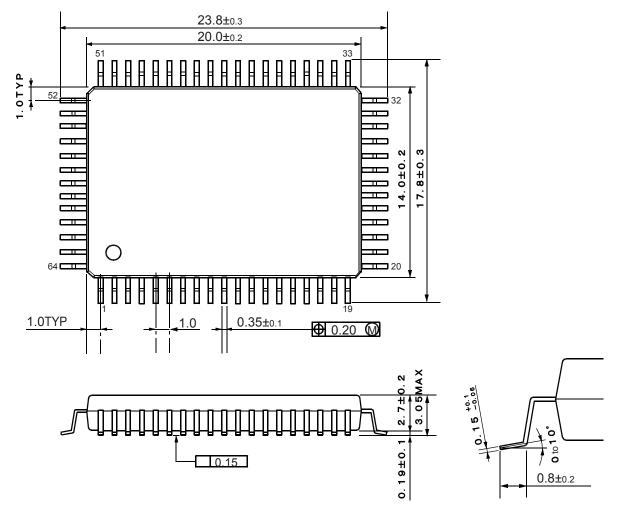

| 7-2. External dimensions of the PCD4521                                                                                                                         |                                                                                                                                              |

| 7-3. External dimensions of the PCD4541                                                                                                                         | 49                                                                                                                                           |

|                                                                                                                                                                 |                                                                                                                                              |

| 8. Electrical characteristics                                                                                                                                   | 50                                                                                                                                           |

|                                                                                                                                                                 |                                                                                                                                              |

| <ul> <li>8. Electrical characteristics</li> <li>8-1. Absolute maximum rating</li> <li>8-2. Recommended operation conditions</li> </ul>                          | 50                                                                                                                                           |

| 8-1. Absolute maximum rating                                                                                                                                    | 50<br>50                                                                                                                                     |

| 8-1. Absolute maximum rating<br>8-2. Recommended operation conditions                                                                                           | 50<br>50<br>50                                                                                                                               |

| <ul><li>8-1. Absolute maximum rating</li><li>8-2. Recommended operation conditions</li><li>8-3. DC characteristics (recommended operating conditions)</li></ul> | 50<br>50<br>50<br>51                                                                                                                         |

| <ul> <li>8-1. Absolute maximum rating</li></ul>                                                                                                                 | 50<br>50<br>50<br>51<br>51                                                                                                                   |

| <ul> <li>8-1. Absolute maximum rating</li> <li>8-2. Recommended operation conditions</li></ul>                                                                  | 50<br>50<br>50<br>51<br>51<br>51                                                                                                             |

| <ul> <li>8-1. Absolute maximum rating</li></ul>                                                                                                                 | 50<br>50<br>50<br>51<br>51<br>51<br>51                                                                                                       |

| <ul> <li>8-1. Absolute maximum rating</li></ul>                                                                                                                 | 50<br>50<br>51<br>51<br>51<br>51<br>51                                                                                                       |

| <ul> <li>8-1. Absolute maximum rating</li></ul>                                                                                                                 | 50<br>50<br>51<br>51<br>51<br>51<br>51<br>52                                                                                                 |

| <ul> <li>8-1. Absolute maximum rating</li></ul>                                                                                                                 | 50<br>50<br>50<br>51<br>51<br>51<br>51<br>51<br>51<br>51<br>51<br>52<br>53                                                                   |

| <ul> <li>8-1. Absolute maximum rating</li></ul>                                                                                                                 | 50<br>50<br>50<br>51<br>51<br>51<br>51<br>51<br>51<br>52<br>52<br>53                                                                         |

| <ul> <li>8-1. Absolute maximum rating</li></ul>                                                                                                                 | 50<br>50<br>50<br>51<br>51<br>51<br>51<br>51<br>51<br>52<br>53<br>53<br>53                                                                   |

| <ul> <li>8-1. Absolute maximum rating</li></ul>                                                                                                                 | 50<br>50<br>50<br>51<br>51<br>51<br>51<br>51<br>51<br>51<br>52<br>53<br>53<br>53<br>53                                                       |

| <ul> <li>8-1. Absolute maximum rating</li></ul>                                                                                                                 | 50<br>50<br>50<br>51<br>51<br>51<br>51<br>51<br>51<br>51<br>52<br>53<br>53<br>53<br>53<br>53<br>53                                           |

| <ul> <li>8-1. Absolute maximum rating</li></ul>                                                                                                                 | 50<br>50<br>50<br>51<br>51<br>51<br>51<br>51<br>51<br>51<br>52<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53                         |

| <ul> <li>8-1. Absolute maximum rating</li></ul>                                                                                                                 | 50<br>50<br>50<br>51<br>51<br>51<br>51<br>51<br>51<br>51<br>52<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>54<br>54                   |

| <ul> <li>8-1. Absolute maximum rating</li></ul>                                                                                                                 | 50<br>50<br>50<br>51<br>51<br>51<br>51<br>51<br>51<br>51<br>52<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>54<br>54<br>54<br>54       |

| <ul> <li>8-1. Absolute maximum rating</li></ul>                                                                                                                 | 50<br>50<br>50<br>51<br>51<br>51<br>51<br>51<br>51<br>51<br>52<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53 |

| 8-5-11. BSY and accel/decel timing                             | . 55 |

|----------------------------------------------------------------|------|

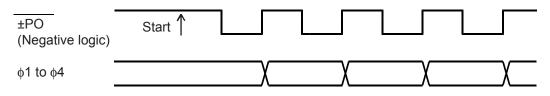

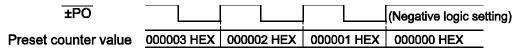

| 8-5-12. Start timing (When $\pm PO$ is set to negative logic)  |      |

| 8-5-13. External start timing                                  | . 56 |

| 8-5-14. Acceleration start timing                              | . 56 |

| 8-5-15. Ramping-down point deceleration initiation timing      | . 57 |

| 8-5-16. Stopping time (When $\pm PO$ is set to negative logic) | . 57 |

| 9. Handling precautions                                        | 58   |

| 9-1. Design precautions                                        | . 58 |

| 9-2. Precautions for transporting and storing LSIs             | . 58 |

| 9-3. Precautions for installation                              | . 58 |

| 9-4. Other precautions                                         | . 59 |

# Appendix

| List of commands                                        | . 60 |

|---------------------------------------------------------|------|

| List of registers                                       | . 61 |

| Monitor list                                            | . 62 |

| Connection examples                                     | . 64 |

| Differences from the PCD4500 (first LSI in this series) | . 67 |

# 1. Outline and features

#### [Outline]

The PCD4511/4521/4541 are excitation control LSIs designed for 2-phase stepper motors. With just one of these LSIs and a stepper motor driver IC (e.g. NP-7026), you can easily construct a stepper motor control system.

Data and commands entered from a CPU enable this LSI to control the speed and position of a stepper motor. Since the LSI has a pulse signal generation circuit, it can also control a motor driver that relies on the number of pulses supplied.

[Features]

- Excitation sequencing output for a 2-phase stepper motor.

- Linear and S-curve acceleration/deceleration control.

- CW and CCW pulse output.

- External start and stop control

- Zero return operation

- Outputs idling pulses

- 400 KPPS maximum output frequency

- Available in single axis (PCD4511), 2-axis (PCD4521), and 4-axis (PCD4541) models.

# 2. Specifications

| Item                                 | Description                                                      |

|--------------------------------------|------------------------------------------------------------------|

| Power source                         | +5V ±10%                                                         |

| Reference clock                      | 4.9152 MHz standard (10 MHz max.)                                |

| Range of settable positioning pulses | 0 to 16,777,215 pulses                                           |

| Range of settable speeds             | 1 to 8,191 steps                                                 |

| Recommended speed magnification      | 1x to 2x (Using a standard 4.9152 MHz clock)                     |

| range*                               | When 1x: will deliver 1 to 8,191 PPS                             |

|                                      | When 2x: will deliver 2 to 16,382 PPS                            |

| Number of registers for setting the  | Two (FL and FH)                                                  |

| speed                                |                                                                  |

| Ramping-down point setting range     | 0 to 65,535 pulses                                               |

| Accel/decel rate setting range       | 2 to 1,023                                                       |

| Typical operations                   | - Continuous operation                                           |

|                                      | <ul> <li>Preset operation (positioning)</li> </ul>               |

|                                      | - Zero return operation                                          |

|                                      | - Timer operation                                                |

| Typical functions                    | <ul> <li>Linear and S-curve acceleration/deceleration</li> </ul> |

|                                      | <ul> <li>Immediate stop and decelerating stop</li> </ul>         |

|                                      | - Speed change                                                   |

|                                      | - Settable ramping-down point                                    |

|                                      | - External start and stop function                               |

|                                      | - Idling pulse output function                                   |

|                                      | - Excitation sequencing output for 2-phase stepper motors        |

|                                      | [Phase signals for unipolar and bipolar motors]                  |

|                                      | [2-2 phase excitation, 1-2 phase excitation phase signals]       |

| Ambient operating temperature        | 0 to +85°C                                                       |

| Storage temperature                  | -40 to +125°C                                                    |

| Package                              | PCD4511: 44-pin QFP                                              |

|                                      | PCD4521: 64-pin QFP                                              |

|                                      | PCD4541: 100-pin QFP                                             |

| Chip design                          | C-MOS                                                            |

\* This value is true when a stepper motor is used within the 24-bit preset counter range.

# 3. Table of registers

| Register<br>No. | Details                                                     | Bit<br>length | R/W  | Setting range<br>( ) = HEX |

|-----------------|-------------------------------------------------------------|---------------|------|----------------------------|

| R0              | Set the preset counter value and check the remaining pulses | 24            | R/W  | 0 to 16, 777, 215 (FFFFF)  |

| R1              | Set the FL speed                                            | 13            | W(R) | 1 to 8, 191 (1FFF)         |

| R2              | Set the FH speed                                            | 13            | W(R) | 1 to 8, 191 (1FFF)         |

| R3              | Set the acceleration/deceleration rate                      | 10            | W(R) | 2 to 1, 023 (3FF)          |

| R4              | Set the magnification rate                                  | 10            | W(R) | 2 to 1, 023 (3FF)          |

| R5              | Set the ramping-down point                                  | 16            | W(R) | 0 to 65, 535 (FFFF)        |

| R6              | Set the number of idling pulses                             | 3             | W(R) | 0 to 7                     |

| R7              | Enter environmental data (PCD4541 only) See Note            | 1             | W(R) | 0 to (1)                   |

\* R/W: Read/Write register

W(R): Write only register. However, reading is possible by enabling the extension monitor. Note: Only the PCD4541 can write a "1" to R7. "0" must be written to this register on the PCD4511 and 4521.

# 4. Hardware description

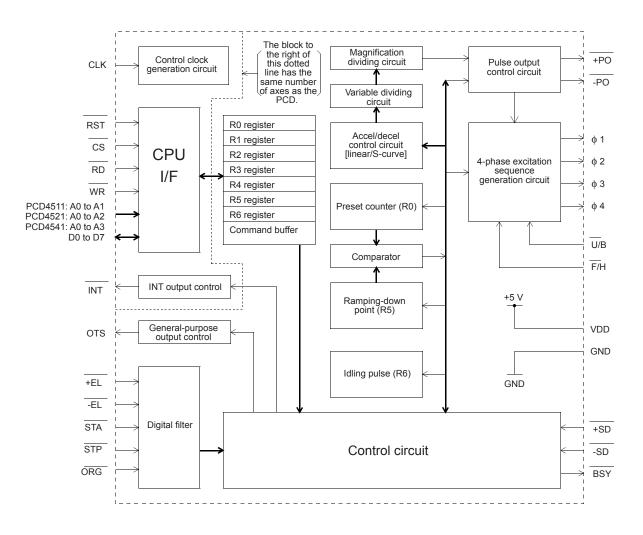

4-1. Circuit block diagram

# 4-2. Terminal assignment diagrams

# 4-2-1. Terminal assignment diagram for the PCD4511

#### 4-2-3. Terminal assignment diagram for the PCD4541

#### 4-3. List of terminals

|                      |          | PCD4511      |            |                                                       |

|----------------------|----------|--------------|------------|-------------------------------------------------------|

| Terminal             | Terminal | Input/output | Logic      | General description                                   |

| number               | name     | · ·          | •          |                                                       |

| 1 to 5               | D0 to D4 | Input/output | Positive   | Data bus signal                                       |

| 6, 10, 20,<br>28, 35 | GND      |              |            | 0 V                                                   |

| 7 to 9               | D5 to D7 | Input/output | Positive   | Data bus signal                                       |

| 11                   | -SD      | Input %      | Negative   | Negative deceleration switch signal                   |

| 12                   | +SD      | Input %      | Negative   | Positive deceleration switch signal                   |

| 13                   | -EL      | Input %      | Negative   | Negative end limit switch signal                      |

| 14                   | +EL      | Input %      | Negative   | Positive end limit switch signal                      |

| 15                   | ORG      | Input %      | Negative   | Zero position limit switch signal                     |

| 16                   | -PO      | Output       | Negative # | Negative pulse                                        |

| 17, 23, 24,<br>39    | VDD      |              |            | +5V±10%                                               |

| 18                   | +PO      | Output       | Negative # | Positive pulse                                        |

| 19                   | BSY      | Output       | Negative   | Running signal                                        |

| 21, 22               | NC       | Output       |            | Test signal                                           |

| 25                   | STA      | Input %      | Negative   | External start signal                                 |

| 26                   | STP      | Input %      | Negative   | Forced stop signal                                    |

| 27                   | Ū/B      | Input %      |            | Select excitation method                              |

|                      |          | •            |            | (unipolar/bipolar)                                    |

| 29                   | F/H      | Input %      |            | Select excitation sequence<br>(2-2 phase / 1-2 phase) |

| 30                   | Φ1       | Output       | Positive   | 1st phase excitation signal                           |

| 31                   | Φ2       | Output       | Positive   | 2nd phase excitation signal                           |

| 32                   | Φ3       | Output       | Positive   | 3rd phase excitation signal                           |

| 33                   | Φ4       | Output       | Positive   | 4th phase excitation signal                           |

| 34                   | OTS      | Output       | Positive   | General-purpose output signal                         |

| 36                   | CLK      | Input        |            | Reference clock                                       |

| 37                   | RST      | Input        | Negative   | Reset signal                                          |

| 38                   | INT      | Output*      | Negative   | Interrupt signal                                      |

| 40                   | CS       | Input        | Negative   | Chip select signal                                    |

| 41, 42               | A1, A0   | Input        | Positive   | Address signal                                        |

| 43                   | WR       | Input        | Negative   | Write signal                                          |

| 44                   | RD       | Input        | Negative   | Read signal                                           |

4-3-1. List of terminals on the PCD4511

- A "\*" in the input/output column means that a pull up resistor is integrated into the open drain output. (These outputs can be wire ORed).

- A "%" in the input/output column means that a pull up resistor is integrated into the input. (To avoid a high impedance state.)

- A "#" in the logic column means that the logic for this signal can be inverted. The condition given refers to the initial status.

- Make sure that all 5 GND terminals are connected and that all 4 VDD terminals are connected.

- Leave both NC terminals open.

| 4-3-2. List of terminals on the P | PCD4521 |

|-----------------------------------|---------|

|-----------------------------------|---------|

| Terminal                         | Terminal | 9 004521     |            |                                                       |

|----------------------------------|----------|--------------|------------|-------------------------------------------------------|

| number                           | name     | Input/output | Logic      | General description                                   |

| 1                                | RST      | Input        | Negative   | Reset signal                                          |

| 2                                | INT      | Output*      | Negative   | Interrupt signal                                      |

| 3                                | CS       | Input        | Negative   | Chip select signal                                    |

| 4                                | WR       | Input        | Negative   | Write signal                                          |

| 5                                |          | Input        | Negative   | Read signal                                           |

| 6, 7, 8                          | A0 to A2 |              | Positive   | Address signal                                        |

| 9                                |          | Input/output | Positive   | Data bus signal                                       |

| 10, 21, 32,<br>42, 52, 62        | GND      |              |            | 0 V                                                   |

|                                  | D1 to D4 | Input/output | Positive   | Data bus signal                                       |

| 15, 26, 27,<br>47, 58, 59,<br>64 | VDD      |              |            | +5V ±10%                                              |

| 16 to 18                         | D5 to D7 | Input/output | Positive   | Data bus signal                                       |

| 19 (X), 40(Y)                    | 0/B      | Input %      |            | Select excitation method<br>(unipolar/bipolar)        |

| 20 (X), 41(Y)                    | F/H      | Input %      |            | Select excitation sequence<br>(2-2 phase / 1-2 phase) |

| 22 (X), 43(Y)                    | Φ1       | Output       | Positive   | 1st phase excitation signal                           |

| 23 (X), 44(Y)                    | Φ2       | Output       | Positive   | 2nd phase excitation signal                           |

| 24 (X), 45(Y)                    | Φ3       | Output       | Positive   | 3rd phase excitation signal                           |

| 25 (X), 46(Y)                    | Φ4       | Output       | Positive   | 4th phase excitation signal                           |

| 28 (X), 48(Y)                    | +PO      | Output       | Negative # | Positive pulse                                        |

| 29 (X), 49(Y)                    | -PO      | Output       | Negative # | Negative pulse                                        |

| 30 (X), 50(Y)                    | BSY      | Output       | Negative   | Running signal                                        |

| 31 (X), 51(Y)                    | OTS      | Output       | Positive   | General-purpose output signal                         |

| 33 (X), 53(Y)                    | STA      | Input %      | Negative   | External start signal                                 |

| 34 (X), 54(Y)                    | STP      | Input %      | Negative   | Forced stop signal                                    |

| 35 (X), 55(Y)                    |          | Input %      | Negative   | Zero position limit switch signal                     |

| 36 (X), 56(Y)                    | +EL      | Input %      | Negative   | Positive end limit switch signal                      |

| 37 (X), 57(Y)                    | -EL      | Input %      | Negative   | Negative end limit switch signal                      |

| 38 (X), 60(Y)                    | +SD      | Input %      | Negative   | Positive deceleration switch signal                   |

| 39 (X), 61(Y)                    | -SD      | Input %      | Negative   | Negative deceleration switch signal                   |

| 63                               | CLK      | Input        |            | Reference clock                                       |

- "X" in the terminal number column is the terminal number for the X axis, "Y" is for the Y axis.

- A "\*" in the input/output column means that a pull up resistor is integrated into the open drain output. (These outputs can be wire ORed.)

- A "%" in the input/output column means that a pull up resistor is integrated into the input. (To avoid a high impedance state.)

- A "#" in the logic column means that the logic for this signal can be inverted. The condition given refers to the initial status.

- Make sure that all 6 GND terminals are connected and that all 7 VDD terminals are connected.

| Terminal number                  | Terminal name | Input/output | Logic      | General description                                   |

|----------------------------------|---------------|--------------|------------|-------------------------------------------------------|

| 1, 2, 3, 4                       | A0 to A3      | Input        | Positive   | Address signal                                        |

| 5                                | INT           | Output*      | Negative   | Interrupt signal                                      |

| 6, 16, 41, 54, 67, 68, 91,<br>95 | VDD           |              |            | +5V ±10%                                              |

| 7 to 14                          | D0 to D7      | Input/output | Positive   | Data bus signal                                       |

| 15, 27, 40, 66, 90, 93           | GND           |              |            | 0 V                                                   |

| 17(X), 35(Y), 62(Z), 82(U)       | BSY           | Output       | Negative   | Running signal                                        |

| 18(X), 36(Y), 63(Z), 83 (U)      | Φ1            | Output       | Positive   | 1st phase excitation signal                           |

| 19(X), 37(Y), 64(Z), 84(U)       | Φ2            | Output       | Positive   | 2nd phase excitation signal                           |

| 20(X), 38(Y), 65(Z), 85(U)       | Φ3            | Output       | Positive   | 3rd phase excitation signal                           |

| 21(X), 39(Y), 69(Z), 86(U)       | Φ4            | Output       | Positive   | 4th phase excitation signal                           |

| 22(X), 42(Y), 70(Z), 87(U)       | +PO           | Output       | Negative # | Positive pulse                                        |

| 23(X), 43(Y), 71(Z), 88(U)       | -PO           | Output       | Negative # | Negative pulse                                        |

| 24(X), 44(Y), 72(Z), 89(U)       | OTS           | Output       | Positive   | General-purpose output signal                         |

| 25(X), 45(Y), 73(Z), 96(U)       | Ū/B           | Input %      |            | Select excitation method<br>(unipolar/bipolar)        |

| 26(X), 46(Y), 74(Z), 97(U)       | F/H           | Input %      |            | Select excitation sequence<br>(2-2 phase / 1-2 phase) |

| 28(X), 47(Y), 55(Z), 75(U)       | STA           | Input %      | Negative   | External start signal                                 |

| 29(X), 48(Y), 56(Z), 76(U)       | STP           | Input %      | Negative   | Forced stop signal                                    |

| 30(X), 49(Y), 57(Z), 77(U)       | ORG           | Input %      | Negative   | Zero position limit switch signal                     |

| 31(X), 50(Y), 58(Z), 78(U)       | +EL           | Input %      | Negative   | Positive end limit switch signal                      |

| 32(X), 51(Y), 59(Z), 79(U)       | -EL           | Input %      | Negative   | Negative end limit switch signal                      |

| 33(X), 52(Y), 60(Z), 80(U)       | +SD           | Input %      | Negative   | Positive deceleration switch signal                   |

| 34(X), 53(Y), 61(Z), 81(U)       | -SD           | Input %      | Negative   | Negative deceleration switch signal                   |

| 92                               | CLK           | Input        |            | Reference clock                                       |

| 94                               | RST           | Input        | Negative   | Reset signal                                          |

| 98                               | CS            | Input        | Negative   | Chip select signal                                    |

| 99                               | RD            | Input        | Negative   | Read signal                                           |

| 100                              | WR            | Input        | Negative   | Write signal                                          |

|                                  |               |              | -          |                                                       |

4-3-3. List of terminals on the PCD4541

- "X" in the terminal number column is the terminal number for the X axis, "Y" is for the Y axis, "Z" is for the Z axis, and "U" refers to the U axis.

- A "\*" in the input/output column means that a pull up resistor is integrated into the open drain output. (These outputs can be wire ORed.)

- A "%" in the input/output column means that a pull up resistor is integrated into the input. (To avoid a high impedance state.)

- A "#" in the logic column means that the logic for this signal can be inverted. The condition given refers to the initial status.

- Make sure that all 6 GND terminals are connected and that all 8 VDD terminals are connected.

#### 4-4. Description of each terminal

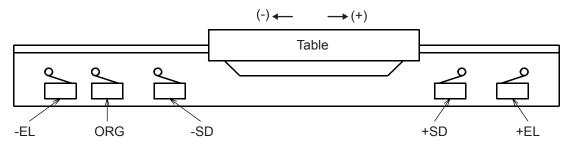

#### 4-4-1. +SD, -SD

Input terminals for deceleration speed switch signals.

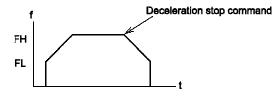

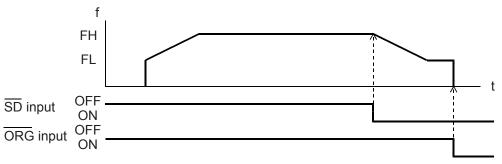

When SD signal control is enabled in the control mode command, and when the SD signal with the same polarity as the current direction of rotation goes LOW while in high-speed operation, the LSI will start to decelerate.

When the SD signal goes HIGH again, the LSI will begin to accelerate again.

#### 4-4-2. +EL, -EL

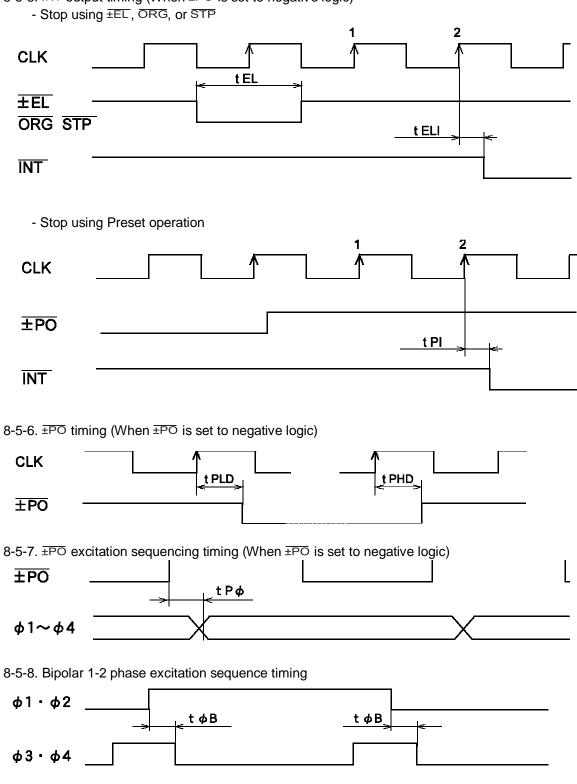

Input terminals for the end limit switch signals.

When the  $\overline{EL}$  signal which has the same polarity as the current direction of motor rotation goes LOW, the LSI will stop the motor immediately. The LSI will not restart the motor, even when this signal goes HIGH again.

If the  $\overline{EL}$  signal is already LOW and an attempt is made to start the motor rotating in that direction, the LSI will not let it start.

When pulse output control is set to "halt output (timer mode)" using the output mode command, the  $\overline{EL}$  signal is disabled.

#### 4-4-3. ORG

Input terminal for the zero position switch signal.

When ORG signal control is enabled (zero position return operation) using the control mode command, and when this signal goes LOW, the motor will stop immediately. Even if this signal goes HIGH again, the LSI not start the motor.

If the ORG signal is already LOW and an attempt is made to start the motor, the LSI will not let it start.

When pulse output control is selected "halt output (timer mode)" using the output mode command, the ORG signal is disabled.

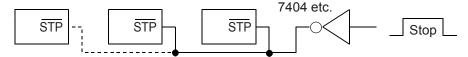

#### 4-4-4. STP

Input terminal for the forced stop signal.

When the  $\overline{STP}$  signal goes LOW, regardless of the rotation direction of the motor, the motor will stop immediately. Even if this signal goes HIGH again, the LSI will not start the motor. If the  $\overline{STP}$  signal is already LOW and an attempt is made to start the motor, the LSI will not let it start.

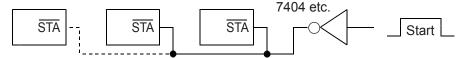

#### 4-4-5. STA

Input terminal for external start signal.

When a start latch command is entered using the start mode command, the motor will start rotation on the leading edge of an STA signal transition from HIGH to LOW.

A signal shorter than 4 cycles of the reference clock is not accepted.

#### 4-4-6. <del>-</del>PO, <u>-</u>PO

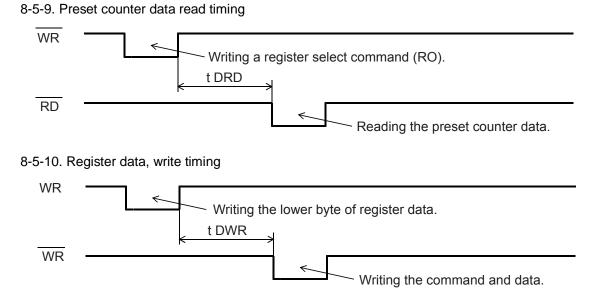

Pulse output terminals.

When the rotation direction is set to positive using the control mode command, the LSI will output pulses at a 50% duty cycle from +PO terminal. When the rotation direction is set to negative using the control mode command, the LSI will output pulses at a 50% duty cycle from -PO terminal.

The logic of the +PO and -PO terminals, and the ON/OFF control of pulse outputs, can be changed using the output mode command.

#### 4-4-7. Φ1, Φ2, Φ3, and Φ4

Excitation signal output terminals for a stepper motor.

The switching of the excitation sequencing signals is synchronized with the output pulses. Using the  $\overline{F}/H$  terminals, you can select between 1-2 phase and 2-2 phase excitation sequencing.

Using the U/B terminals, you can select between unipolar and bipolar excitation sequencing. When pulse output control is set to "halt output (timer mode)" using the output mode command, the excitation sequencing cannot be changed.

Using the output mode command, the excitation signal can be masked (to make all of the terminals  $\Phi$ 1 to 4 LOW).

### 4-4-8. Ū/B

Terminal for selecting the excitation method.

Select unipolar excitation with a LOW or bipolar excitation sequencing with a HIGH on this terminal. Connect to GND or VDD.

This terminal is latched when reset.

For details about the sequence for reading this terminal, see "6-1. Excitation sequencing for stepper motors."

# 4-4-9. F/H

Terminal for selecting the excitation sequence.

2-2 phase and 1-2 phase are typical excitation sequences for 2-phase stepper motors. Select the sequence using this terminal.

Select 2-2 phase excitation with a LOW and 1-2 phase excitation sequencing with a HIGH. Connect to GND or VDD.

For details about the sequence for reading this terminal, see "6-1. Excitation sequencing for stepper motors."

# 4-4-10. OTS

General-purpose output terminal.

This terminal can be used as an excitation ON/OFF control signal for a motor driver IC. This terminal can be controlled by a CPU. When bit 4 of the control mode command is "1" this terminal is HIGH, when it is "0" the terminal is LOW.

#### 4-4-11. INT

Output terminal for sending an interrupt request signal to a CPU.

This terminal will go LOW when the LSI requests an interrupt. Set this signal HIGH using the interrupt condition setting command. This terminal can also be masked.

By setting the start mode command, the LSI can be set to output an  $\overline{INT}$  request signal when stopping the motor. Using this terminal, you can call for an interrupt when the preset operation is complete, or when operation is stopped by the  $\overline{ORG}$  signal,  $\overline{+EL}$  or  $\overline{-EL}$  signal, or the  $\overline{STP}$  signal. An interrupt can also be requested by a deceleration stop or an immediate stop command.

Using the register select command, an INT request signal can be output when starting deceleration from the ramping-down point or from an external signal.

When using PCD series LSIs, the INT terminals of a number of chips can be wire ORed. Install an external pull up resistor (5 to 10 K ohms).

# 4-4-12. BSY

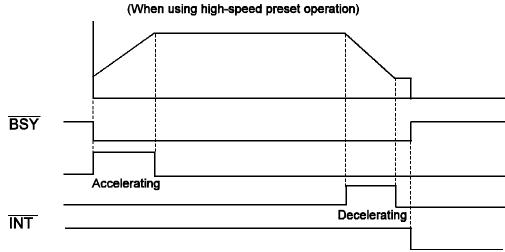

Operation status monitor terminal.

When the LSI is in operation, the signal from this terminal goes LOW.

This terminal can be used to check the operation or to provide current to the motor and force it to remain stopped.

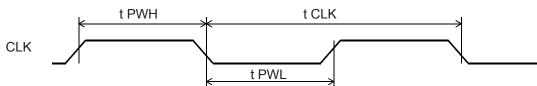

#### 4-4-13. CLK

Input terminal for the reference clock.

Reference clock precision affects the output pulse precision. Besides affecting the output pulses, it also affects the input sensitivity of the start timing signal, STA, ORG, EL and STP signals, as well as read and write timing. Make sure that only a CMOS level input is applied to the CLK terminal.

# 4-4-14. RST

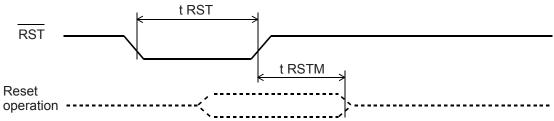

Reset signal input terminal. Bring this terminal LOW for 3 reference clock pulses to reset the LSI. For details about the initial status after a reset, see "4-6. Initial status."

#### 4-4-15. CS

Chip select signal input terminal

Bring this terminal LOW to enable  $\overline{RD}$  and  $\overline{WR}$  signals, which will allow reading and writing to the CPU.

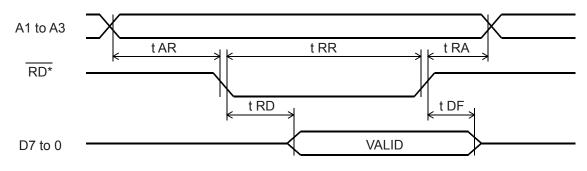

#### 4-4-16. RD

Read signal input terminal

Bring this terminal and the  $\overline{CS}$  terminal LOW to output the contents of the specified register on data bus lines D0 to D7.

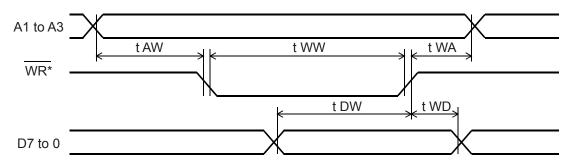

# 4-4-17. WR

Write signal input terminal

Bring this terminal and the  $\overline{CS}$  terminal LOW to write the contents of data bus lines D0 to D7 into the LSI. The lines will be read when the  $\overline{WR}$  signal changes from LOW to HIGH.

# 4-4-18. A0, A1, A2, and A3

Address signal input terminals.

The LSI uses the A0 and A1 terminals to assign use of the data bus to the command buffer, and to the upper, middle, and lower areas of register data.

On the PCD4521 and 4541, terminals A2 and A3 are used to select the axis to control. Normally, this terminal is connected to the lowest bit on the CPU address bus.

#### 4-4-19. D0 to D7

Input and output terminals for the tri-state data bus.

#### 4-4-20. VDD and GND

Power supply terminals.

Supply +5VDC  $\pm$ 10% to the VDD terminals. Make sure to connect all of the power supply terminals.

# 4-4-21. NC [PCD4511 only]

Output terminal for testing. Leave this terminal open.

#### 4-5. Initial (reset) status

| Item                                           | Initial (reset) status |

|------------------------------------------------|------------------------|

| Internal registers (R0 to R6)                  | All zeros              |

| Start mode command                             | 00 HEX                 |

| Control mode command                           | 40 HEX                 |

| Register select command                        | 80 HEX                 |

| Qutput mode command                            | C0 HEX                 |

| INT terminal                                   | Н                      |

| Terminals D0 to D7                             | High impedance         |

| Ø 1, Ø 2, Ø 3, and Ø 4 [Ū/B terminal = when L] | H, L, L, H             |

| Ø 1, Ø 2, Ø 3, and Ø 4 [Ū/B terminal = when H] | H, L, L, L             |

| ±PO terminal                                   | Н                      |

| BSY terminal                                   | Н                      |

| OTS terminal                                   | L                      |

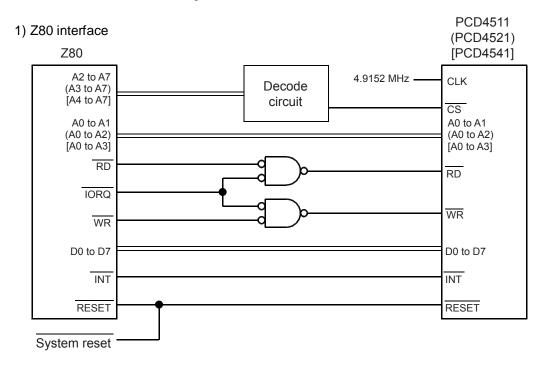

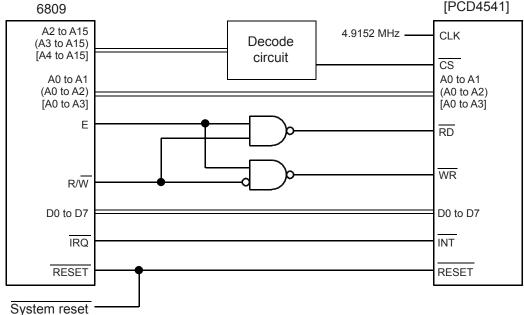

#### 4-6. CPU interface circuit block diagram

# 2) 6809 interface

PCD4511 (PCD4521) [PCD4541]

#### 4-7. Precautions for designing hardware

#### 4-7-1. Input terminals

Only the CLK terminal requires a CMOS level input. Be careful when connecting this terminal.

(For reset operations, the internal processing may require up to three reference clock cycles. When imposing a LOW on the  $\overline{RST}$  terminal make sure it lasts more than 3 reference clock cycles.)

If you want to wire-OR the INT terminal or input the switch signal terminals with open collectors, we recommend installing a pull up resistor.

(The  $\pm$ EL,  $\pm$ SD, ORG, STA, STP, and INT terminals on the PCD4511 have pull-up resistors built in. However these are for preventing a high impedance condition. Since their resistance values are high [25 K to 500 K ohm], we recommend installing external pull-up resistors [5-K to 10-K ohms].)

For safe operation, we recommend using a multiple-layer PC board with a separate power layer.

#### 4-7-2. Excitation sequencing

The description of the excitation sequence required by a particular bipolar 1-2 phase stepper motor driver IC may be different.

(This LSI's excitation sequence is designed for our NP-7024M (7026M) unipolar driver IC, and our NP-2918 bipolar driver IC. These are common excitation sequences. However, bipolar excitation sequence requirements may vary with different driver IC manufacturers. Driver ICs which can use the following excitation sequence may be used. In this case, contact the driver IC manufacturer to verify the suitability of our excitation sequence.)

| Ex.1      |                                          |   |   |   |   |   |   |   |   |

|-----------|------------------------------------------|---|---|---|---|---|---|---|---|

|           | 1-2 phase excitation for bipolar drivers |   |   |   |   |   |   |   |   |

| STEP ->   | 0                                        | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 0 |

| Α         | Н                                        | Н | Н | L | L | L | L | L | Н |

| DISABLE A | L                                        | L | L | Н | L | L | L | Н | L |

| В         | L                                        | L | Н | Н | Н | L | L | L | L |

| DISABLE B | L                                        | Н | L | L | L | Н | L | L | L |

Ex. 2

|           | 1-2 phase excitation for bipolar drivers |   |   |   |   |   |   |   |   |

|-----------|------------------------------------------|---|---|---|---|---|---|---|---|

| STEP ->   | 0                                        | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 0 |

| А         | Н                                        | Н | Н | Н | L | L | L | Н | Н |

| DISABLE A | L                                        | L | L | н | L | L | L | I | L |

| В         | L                                        | Η | H | н | н | Н | L | L | L |

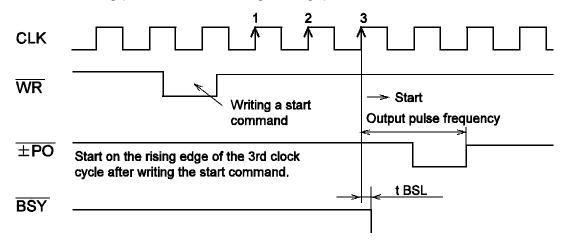

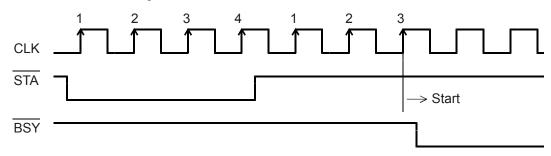

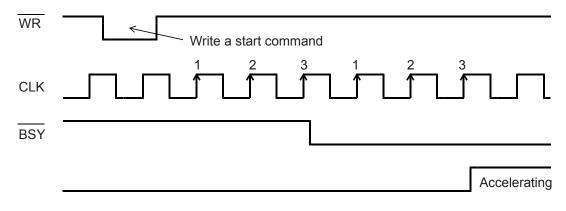

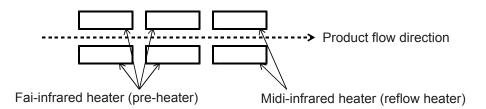

| DISABLE B | L                                        | Н | L | L | L | Н | L | L | L |